VLSI circuit design for low power:

The growing market of portable (e.g., cellular phones, gaming consoles, etc.), battery-powered electronic systems demands microelectronic circuits design with ultra low power dissipation. As the integration, size, and complexity of the chips continue to increase, the difficulty in providing adequate cooling might either add significant cost or limit the functionality of the computing systems which make use of those integrated circuits. As the technology node scales down to 65nm there is not much increase in dynamic power dissipation. However the static or leakage power is same as or exceeds the dynamic power beyond 65nm technology node.

Hence the techniques to reduce power dissipation is not limited to dynamic power. In this article we discuss circuit and logic design approaches to minimize Dynamic, Leakage and Short Circuit power dissipation. Power optimization in a processor can be achieved at various abstract levels . System/Algorithm/Architecture have a large potential for power saving even these techniques tend to saturate as we integrate more functionality on an IC. So optimization at Circuit and Technology level is also very important for miniaturization of ICs.

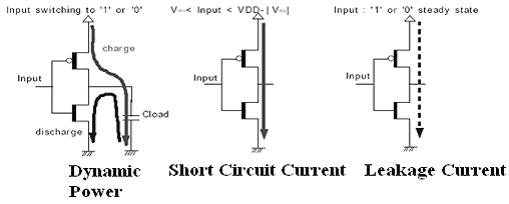

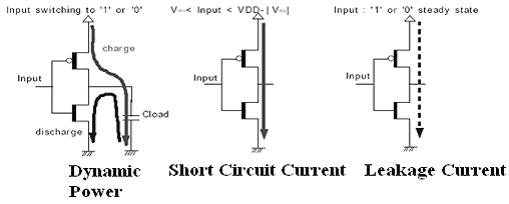

Total Power dissipated in a CMOS circuit is sum total of dynamic power,short circuit power and static or leakage power. Design for low-power implies the ability to reduce all three components of power consumption in CMOS circuits during the development of a low power electronic product. In the sections to follow we summerize the most widely used circuit techniques to reduce each of these components of power in a standard CMOS design.

Dynamic Power Suppression

Dynamic/Switching power is due to charging and discharging of load capacitors driven by the circuit. Supply voltage scaling has been the most adopted approach to power optimization, since it normally yields considerable power savings due to the quadratic dependence of switching/dynamic power PSwitching on supply voltage VDD. However lowering the supply voltage affects circuit speed which is the major short-coming of this approach. So both design and technological solutions must be applied to compensate the decrease in circuit performance introduced by reduced voltage. Some of the techniques often used to reduce dynamic power are described below.

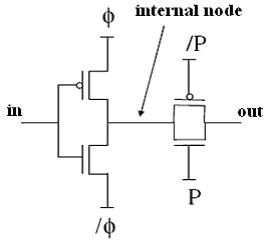

Adiabatic Circuits

In adiabatic circuits instead of dissipating the power is reused. By externally controlling the length and shape of signal transitions energy spent to flip a bit can be reduced to very small values. Since diodes are thermodynamically irreversible they are not used in the design of Adiabatic Logic. MOSFETs should not be turned ON when there is significant potential difference between source and drain. And should not be turnoff when there is a significant current flowing through the device.